场效应晶体管(Field-Effect Transistor)是当代计算机处理器的核心。自从上世纪60年代以来,一块典型处理器中的晶体管的数量便以摩尔定律的速度指数增加。通过减小单个器件的尺寸,越来越多的晶体管可以被封装到一块芯片中,与此同时,芯片的性能也越来越好,成本越来越低。

硅基微电子工艺的持续改进驱动了过去半个多世纪以来集成电路的指数级增长。在苹果公司2020年9月的发布会上,苹果公司芯片架构副总裁Tim Millet已经发布了苹果基于5nm制程的A14仿生处理器。

然而时至今日,随着硅基晶体管的尺寸进入了亚10纳米时代,硅基微电子工艺发展面临的技术挑战和瓶颈也愈发困难。因此,为未来的处理器芯片探索新型器件几何构型和新型沟道制造材料的需求迫在眉睫。

由于现在的芯片制程在纳米尺度,未来如果要进一步提升芯片的密度和性能,势必要求我们研发在埃米尺度上的晶体管。由于埃米尺度也正是单个原子半径的经典大小,因此,芯片的下一步发展方向将由现在的纳米级制程进入到原子级制程,即下一代芯片将从现在的“纳米时代”进入到“原子时代”。

对于如何在原子尺度上设计并制造芯片这一问题,学界和业界普遍认为,具有单原子厚度的二维材料将为未来芯片“原子时代”的进一步发展提供新的范式。特别是近十年以来,学术界和工业界对以石墨烯、氮化硼、过渡金属二硫化物、黑磷等为代表的一批具有二维材料广泛和深入的研究,为我们掌握、操控并制造原子级厚度的器件提供了扎实的数据库和成熟的方法。

近期,来自中国湖南大学、韩国三星高等技术研究院和美国加州洛杉矶分校的研究人员以Promises and prospects of two-dimensional transistors为题在Nature发表综述文章,该篇文章主要介绍了如下内容:

1、讨论了对晶体管操作非常重要的关键材料参数,并将它们与二维和传统三维半导体进行比较。

2、分析了过去研究人员在评估二维晶体管性能时经常误用的一些指标,包括载流子迁移率和半导体材料的接触电阻。

3、讨论了精确测量和正确评价二维晶体管的基本要求,并主张饱和或通态电流密度作为一个更准确的表征二维半导体性能的参数。

4、总结了推动二维晶体管极限的途径、lab到fab过渡的关键技术障碍以及由此产生的潜在机遇。

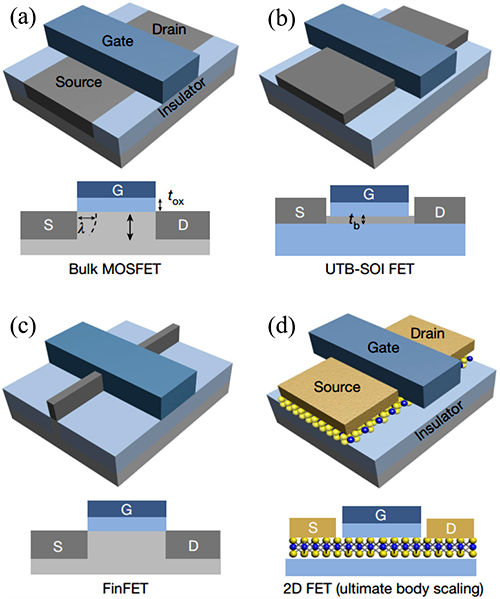

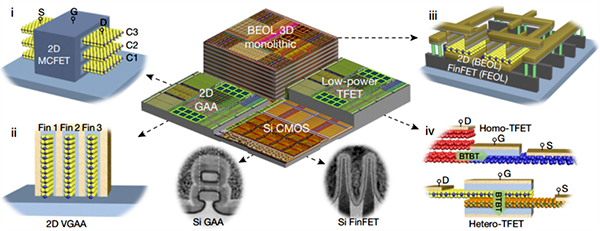

如图1所示,场效应晶体管是一种由源极(Source), 栅极(Gate)和漏极(Drain)构成的电子开关。介于源极和漏极之间半导体沟道电导的开关状态可以由栅极来调控,其中栅极通过静电作用耦合在很薄的介质层上。因此,一个典型的薄膜场效应晶体管的开关状态可以由三终端器件中的静电作用来调控。

图1 场效应晶体管(Field-Effect Transistor)的发展演进

图源:Nature 591,43(2021)(Figure.1)

从历史上来说,芯片技术节点以其物理门的特征尺度来命名。比如,半导体产业界于1996年提出了超薄绝缘体场效应晶体管和鳍式场效应晶体管来实现亚25nm节点的芯片。这些器件结构的采用成功地将摩尔定律扩展到10纳米以下的技术节点。

需要注意的是,现在芯片技术节点的命名已经失去了它的历史物理意义(物理门长度),而仅仅作为一个“市场名称”,指的是特定一代的芯片技术。例如,目前市场上先进的10nm节点的英特尔技术目前在生产的芯片特征尺寸为:一个物理门宽度为18nm,一个半门间距为27nm,鳍片宽度为7nm。

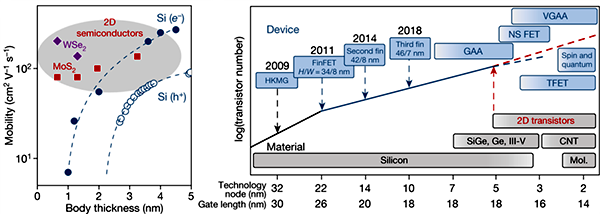

摩尔定律的发展需要产业界进一步降低结芯片的鳍宽度,包括有限的厚度变化、表面粗糙度和不可避免的表面悬挂键等这些困难的挑战。对于传统的三维晶体管来说,晶体管厚度的持续减小会导致载流子迁移率(μ)的大幅降低。特别是,当体厚度低于5nm时,由于厚度波动诱导的散射,迁移率理论上以芯片的鳍宽度的六次方进行衰减,这对晶体管尺寸的持续减小构成了一个临界限制。

如图2所示,随着厚度的减小,传统硅基体材料载流子迁移率会而急剧降低,但是以过渡金属二硫化物为代表的二维半导体材料的载流子迁移率受厚度影响极小,基本保持稳定。所以,二维材料不仅可以实现原子级厚度的沟道,还可以在极小的厚度和体积下保持优良的电学特性。因此,二维材料是芯片进入亚5 nm技术节点时代的强力候选器件。

图2 晶体管发展演进不同阶段所采用的不同工艺技术

图源:Nature 591,43(2021)(Figure.1)

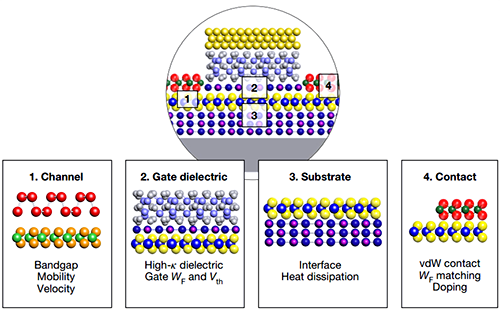

作者认为,在二维半导体材料过去的发展中,研究人员常常误用一些性能指标评估二维晶体管性能,如二维材料载流子迁移率和接触电阻。同时针对这些问题,文章讨论了精确测量和正确评价二维晶体管的基本要求,作者认为我们应该采用通态电流密度作为一个更直接的表征二维半导体性能的参数。

图3 对于器件设计的优化应重点关注的性能指标

图源:Nature 591,43(2021)(Box.1)

尽管二维晶体管具有巨大的潜力,在基础材料和器件研究方面也取得了巨大的进展,但是作者认为,在我们将二维晶体管从基础研究拓展到产业应用的过程中仍存在许多挑战:

1、如何客观准确二维晶体管性能的关键技术指标;

2、仍需要探索大规模、均匀、可重复合成制备二维半导体材料的可靠方法;

3、如何使集成过程中用到的材料对半导体工艺的兼容;

4、探索二维半导体材料的“杀手级应用”,而非片面追求对传统硅基材料的完全取代。

图4 从实验室到晶圆厂的过渡以及行业前景

图源:Nature 591,43(2021)(Figure.4)

如上所述,二维晶体管的一个主要优点是其原子薄的通道,可以减轻短通道效应。然而,在目前的芯片技术中,使用二维晶体管能在多大程度上提高性能仍然没有明确的答案。考虑到硅技术的巨大投资和成熟发展,以及制造二维晶体管所需的许多非常规工艺,在可预见的未来,二维半导体不太可能完全取代硅。相反,二维晶体管的机会在于互补很难通过硅材料实现的性能。

二维材料一个潜在的“杀手级应用”是通过顺序集成过程在同一晶圆上制造多层材料、设备或电路的单片三维集成。

在材料层面,二维晶体固有的独立和悬浮无键特性使它们非常适合多层集成,而不影响每一层的电子性能和器件性能。在器件层面,基于二维的多通道场效应晶体管可以通过叠加由电介质和栅电极分隔的二维单层或垂直生长的二维半导体单层鳍式场效应晶体管来实现,以其优良的门控、高驱动电流和集成密度实现门-全能(GAA)或垂直门-全能(VGAA)二维器件。

在电路层面,不同的二维层可以整体集成,相邻层通过后端线(BEOL)工艺中的孔或沟槽连接,从而实现比传统平面芯片更高的电路密度和更好的设计灵活性。

二维晶体管的另一个新兴机会可能在于新兴的柔性电子产品。目前这一领域被有机半导体所主导。然而,有机半导体的低载流子迁移率限制了驱动电流,阻碍了它们在需要高速操作的领域中的应用(例如,射频识别或处理器)。凭借高载流子迁移率、前所未有的灵活性、低集成温度和环境稳定性的独特组合,二维晶体管可以提供一整代具有柔性、可折叠的高速柔性电子产品。

最后,文章作者认为,尽管二维晶体管产业化道路依然困难重重,但在二维晶体管的晶圆尺度处理和工业尝试上似乎没有根本性的、物理原理上的障碍。

一项前沿技术从实验室到生产车间的成功转变需要多方的共同努力,包括:

◆化学家和材料科学家来合成和评估这些原子级薄材料,用更多的可量化的材料参数来稳定表征其晶圆尺度上的质量;

◆物理学家发展适当的器件模型来描述表面主导的二维半导体中的载流子注入和输运;电气工程师评估和验证设备的更有意义的性能指标、设计和实施集成战略与当前硅电子;

◆所有利益相关者,包括学术研究人员,材料供应商,半导体公司或财团。一旦合成、制造、集成和特性完全标准化并在晶圆规模上进行,高产量分析和可靠性评估将是工业应用的关键。在此之后,持续不断的工程优化将使类似于我们在硅技术中看到的改进成为可能。

文章的作者并不认为微电子学中会突然出现二维晶体管。相反,一种特殊的互补利基应用可能首先出现,如单片三维集成芯片或柔性射频晶体管。鉴于二维晶体管的历史很短,文章作者相信二维材料从实验室到芯片的产业化转变才刚刚开始,并将继续在技术的广度和深度上不断扩展,从而最终为整个人类社会带来巨大的利益。

作者:Blair(西湖大学,博士生)